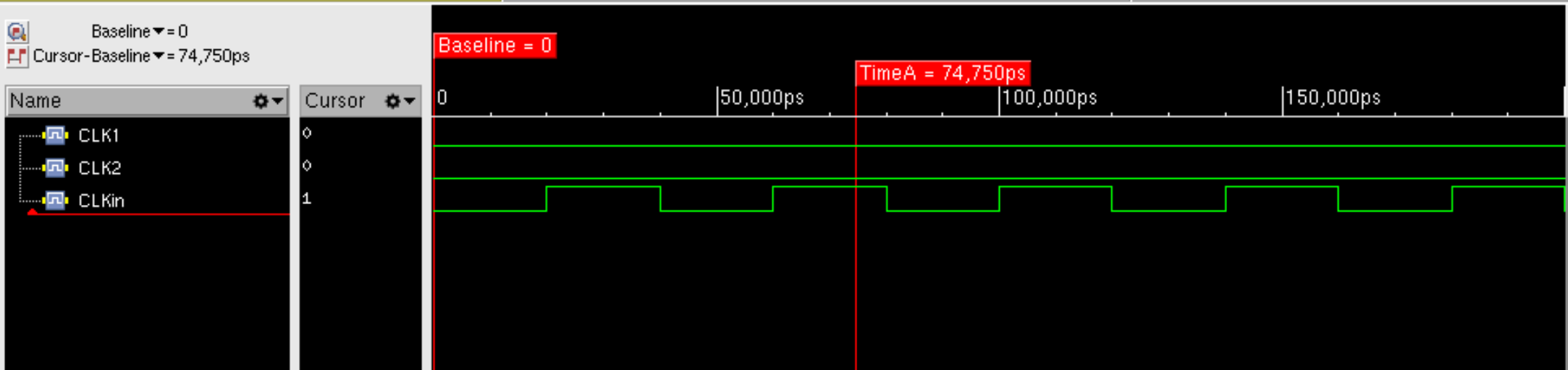

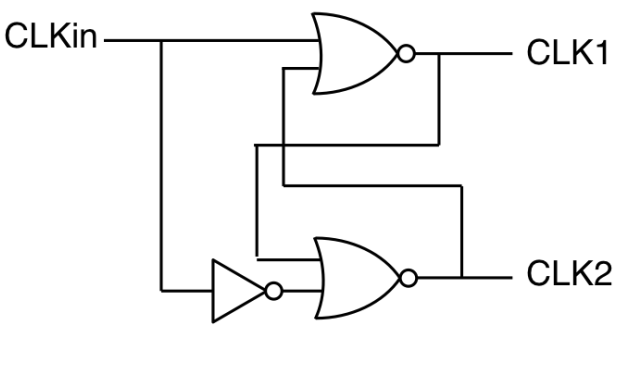

I have to use combinational logic to write Verilog for a circuit schematic. However, my output registers, CLK1 and CLK2, do not change and are stuck at the initial values. What is causing this bug? Here is the code and output:

//Verilog HDL for "HW8", "ClockCircuit" "functional" `resetall `celldefine `delay_mode_path `timescale 1ns / 10ps module ClockCircuit ( input wire CLKin, output reg CLK1, output reg CLK2 ); initial begin CLK1 = 0; CLK2 = 0; end // Intermediate signals wire inv_output; wire nor1_output; wire nor2_output; // Instantiate the inverter inv_1 inv ( CLKin, inv_output ); // Instantiate the first NOR gate nor_2 nor16 ( CLKin, nor2_output, nor1_output ); // Instantiate the second NOR gate nor_2 nor2 ( nor1_output, inv_output, nor2_output ); // Drive the outputs using procedural blocks always @(posedge CLKin) begin CLK1 <= nor1_output; CLK2 <= nor2_output; end endmodule `endcelldefine The circuit I'm trying to create is here: